- 您现在的位置:买卖IC网 > Sheet目录362799 > Eval-AD1940EB (Analog Devices, Inc.) SigmaDSP-TM Multichannel 28-Bit Audio Processor

AD1940

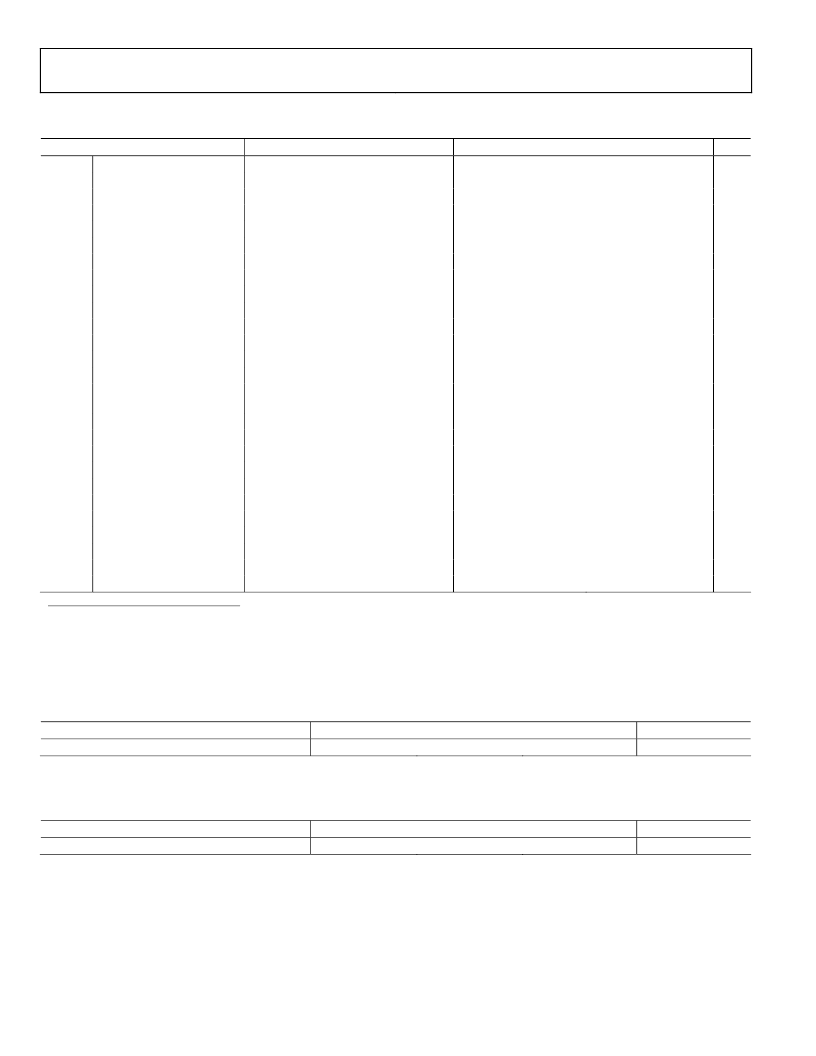

DIGITAL TIMING

Table 5 Digital Timing

1

Parameter

t

MP

MCLK Period

t

MP

MCLK Period

t

MP

MCLK Period

t

MP

MCLK Period

t

MP

MCLK Period

t

MDC

MCLK Duty Cycle

t

BIL

BCLK_IN LO Pulse Width

t

BIH

BCLK_IN HI Pulse Width

t

LIS

LRCLK_IN Setup

t

LIH

LRCLK_IN Hold

t

SIS

SDATA_INx Setup

t

SIH

SDATA_INx Hold

t

LOS

LRCLK_OUTx Setup

t

LOH

LRCLK_OUTx Hold

BCLK_OUTx Falling to

LRCLK_OUTx Timing Skew

t

SODS

SDATA_OUTx Delay

t

SODM

SDATA_OUTx Delay

t

CCPL

CCLK Pulse Width LO

t

CCPH

CCLK Pulse Width HI

t

CLS

CLATCH Setup

t

CLH

CLATCH Hold

t

CLPH

CLATCH Pulse Width HI

t

CDS

CDATA Setup

t

CDH

CDATA Hold

t

COD

COUT Delay

t

RLPW

RESETB LO Pulse Width

Rev. 0 | Page 4 of 32

Comments

512 f

S

mode

384 f

S

mode

256 f

S

mode

64 f

S

mode

Bypass mode

Bypass mode

To BCLK_IN rising

From BCLK_IN rising

To BCLK_IN rising

From BCLK_IN rising

Slave mode

Slave mode

Min

36

48

73

291

12

40

4

2

12

0

3

2

2

2

Max

244

366

488

1953

60

Unit

ns

ns

ns

ns

ns

%

ns

ns

ns

ns

ns

ns

ns

ns

t

TS

2

ns

Slave mode, from BCLK_OUTx falling

Master mode, from BCLK_OUTx falling

To CCLK rising

From CCLK rising

To CCLK rising

From CCLK rising

From CCLK rising

1 × INTMCLK (14)

2

1 × INTMCLK (14)

2

0

2 × INTMCLK + 4 (32)

2

2 × INTMCLK (28)

2

0

2 × INTMCLK + 2 (30)

2

10

17

17

4 × INTMCLK +18 (74)

2

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

1

All timing specifications are given for the default (I

2

S) states of the serial input control port and the serial output control ports. See

2

These specifications are based on the internal master clock period in a specific application. In normal operation, the master clock runs at 1,536 × f

s

, so the internal master

clock at f

s

= 48 kHz has a 14 ns period. The values in parentheses are the timing values for f

s

= 48 kHz.

.

Table 32

PLL

Table 6.

Parameter

Lock Time

Min

Typ

3

Max

20

Unit

ms

REGULATOR

Table 7.

Parameter

VSENSE Output Voltage

Min

2.25

Typ

2.5

Max

2.68

Unit

V

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-AD1953EB

16-bit fixed point DSP with Flash

EVAL-AD1958EB

PLL/Multibit DAC

EVAL-AD1959EB

PLL/Multibit DAC

EVAL-AD1974EB

4 ADC with PLL, 192 kHz, 24-Bit Codec

EVAl-AD1974EBZ

4 ADC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1990EB

Audio Switching Amplifier

EVAL-AD1992EB

Audio Switching Amplifier

EVAL-AD1994EB

Audio Switching Amplifier

相关代理商/技术参数

EVAL-AD1940MINIB

制造商:Analog Devices 功能描述:SIGMADSP EVAL BD - Bulk 制造商:Rochester Electronics LLC 功能描述:

EVAL-AD1940MINIBZ

功能描述:BOARD EVAL AD1940 MINI SIGMADSP RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:SigmaDSP® 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-AD1941EB

制造商:Analog Devices 功能描述:EVAL BD SIGMADSPMULTICHANAUDIO PROCESSOR - Bulk

EVAL-AD1953EB

制造商:Analog Devices 功能描述:EVAL BRD FOR 3 CH 24 BIT SIG-PROCESS DAC - Bulk 制造商:Analog Devices 功能描述:EVALUATION KIT ((NS))

EVAL-AD1953EBZ

制造商:Analog Devices 功能描述:EVAL BRD FOR 3 CH 24 BIT SIG-PROCESS DAC - Bulk

EVAL-AD1954EB

制造商:Rochester Electronics LLC 功能描述:EVAL BRD FOR 3 CH 24 BIT SIG-PROCESS DAC - Bulk 制造商:Analog Devices 功能描述:

EVAL-AD1955EB

制造商:Analog Devices 功能描述:Evaluation Board For AD1955 制造商:Analog Devices 功能描述:EVAL BOARD FOR 24 BIT 192KHZ DAC 120 DB - Bulk 制造商:Rochester Electronics LLC 功能描述:EVAL BOARD FOR 24 BIT 192KHZ DAC 120 DB - Bulk

EVAL-AD1955EBZ

功能描述:BOARD EVAL FOR AD1955 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581